# 東海大學電機工程學系

## 碩士論文

0.18μm 2GHz 互補式金氧半射頻開關之研究設計

Study on 0.18µm 2GHz CMOS RF Switch Circuit

研究生:劉中泰

指導教授:陳家豪 博士

中華民國 九十八 年 七 月

# 0.18μm 2GHz 互補式金氧半射頻開關之研究設計

Study on 0.18µm 2GHz CMOS RF Switch Circuit

研究生:劉中泰 Student: Chungn-Tai Liu

指導教授:陳家豪 博士 Advisor: Dr. Ja-Hao Chen

東海大學 電機工程學系 碩士論文

Department of Electrical Engineering

Tunghai University

Taichung, Taiwan, R.O.C.

Thesis for Master of Science

June, 2009

中華民國 九十八 年 七 月

ı

# 東海大學電機工程學系碩士學位考試委員審定書

電機工程學系研究所<u>劉中泰</u>君所提之論文中文: 0.18 µ m 2GHz 互補式金氧半射頻開關之研究設計

英文: Study on 0.18μm 2GHz CMOS RF Switch Circuit

經本考試委員會審查,符合碩士資格標準。

學位考試委員會 召集人: 菜菜 艺 (簽章)

委 員:

好游杰

中華民國 98 年 07 月 21 日

# 0.18 μm 2GHz 互補式金氧半射頻開關之 研究設計

研究生:劉中泰 指導教授:陳家豪博士

東海大學電機工程學系

## 摘要

近年來矽半導體製程、電腦輔助設計軟體、以及電路設計技巧的 進步,已讓數位與類比電路的整合度大大提高,反觀射頻電路預做整 合的話,仍有許多困難要克服,目前有許多無法整合的高頻電路中, 如射頻濾波器、功率放大器以及射頻開關等電路。其中射頻開關不能 與系統整合的原因,主要是以插入損耗(insertion loss)過高以及功 率承載(power handling)能力低,這些問題的產生主要是矽基板具導 電性,造成訊號會從基板流失。本論文預使用TSMC 0.18μm 1P6M CMOS 製程結合微機電後製程的使用將射頻開關整合入矽晶片。製作高Q電 感,作阻抗匹配,降低插入損耗。其中利用微機電製程蝕刻電路中電 感元件、傳輸線下方的矽基板使其懸空,減少電路的插入損耗,並利 用ADS(Advanced Design System) Momentum[16]模擬所設計的電路, 可得知使用微機電製程蝕刻矽基板[9]可以減少23.7%的插入損耗。而 開關TX端經ADS模擬後功率承載(Pin-1dB)=27.390dBm、插入損耗 (insertion loss)=0.538dB •

# Study on 0.18µm 2GHz CMOS RF Switch Circuit

Student: Chungn-Tai Liu Advisor: Dr. Ja-Hao Chen

Department of Electrical Engineering

Tunghai University, Taichung, Taiwan, R.O.C

#### **Abstract**

In past years, silicon-base semiconductor process, computer-aided design tools, and circuit design skills have all made great progress, and it makes the high integration between digital and analog circuits. However, it is difficult to integrate with radio frequency (RF) circuits, such as RF filter, RF power amplifier, and RF switch. Among those RF circuits, the reasons of that RF switch could not be integrated in system are high insertion loss and low power handling. Those issues occur because the silicon substrate is conductance material inducing power loss. This work use TSMC 0.18µm 1P6M CMOS process and Micro-electro-mechanical Systems (MEMS) post-process to integrate with RF switch on a silicon chip. MEMS post-process is used to etch bulk[9] of the inductance device and transmission line to reduce insertion loss of the switch circuit. Using ADS(Advanced Design System) Momentum[16] to simulate switch circuit and the insertion loss would be reduced 23.7%. The TX node of the switch circuit use ADS Momentum to simulate power handling P1dB=27.390dBm, insertion loss=0.538dB.

### 誌謝

首先感謝我的指導教授陳家豪老師,不僅提供研究上一切的資源與指導,也給予我在射頻電路領域中自由的學習與揮灑的空間,由於老師的鼓勵與支持,方能使我的碩士論文順利完成。並感謝蔡榮昱、林維亮、邱瑞杰三位口試委員於口試期間,能不吝予批評指教,讓論文能修正更加完整。在實驗室的同伴中,首先須感謝博偉、政筌、心旋這三位同學,不論在課業上或生活上的互相鼓勵與關心,一起撐過這充實的兩年時光。也非常謝謝實驗室的學弟正倫與仕翔,於口試中大力的幫忙與支持,讓我有充分的時間來準備。還有其他實驗室的同學,感謝你們陪我在碩士兩年中的點點滴滴。謝謝你們在生活上幫忙與照顧,讓我可以順利地完成我的目標。

# 目 錄

| 芽 | 5-5  | 阜     | 緒   | 論         | • • • |    |           | • • | • • • |       |     | • •   |     | <br> | <br>    | 1   |

|---|------|-------|-----|-----------|-------|----|-----------|-----|-------|-------|-----|-------|-----|------|---------|-----|

| 芽 | 5二三  | 阜     | 開   | 關電        | 電路    | 3原 | 理言        | 說明  | 月     |       |     | • • • | • • | <br> | <br>    | 6   |

|   | 2. 1 | 開關    | 電   | 路功        | 能     | 既述 |           |     | · • • |       | • • |       |     | <br> | <br>    | 6   |

|   | 2.2  | 開關    | 設   | 計原        | 理     | 與分 | 類.        |     |       |       | • • |       |     | <br> | <br>    | 7   |

| 芽 | 三三   | 章     | 微   | 機冒        | 包技    | 術  | 介系        | 召   |       |       | • • |       |     | <br> | <br>. 1 | 1   |

|   | 3. 1 | 微機    | 電   | 作用        | 說明    | 月  |           |     |       | • • • |     |       |     | <br> | <br>. 1 | . 1 |

|   | 3. 2 | 微機    | 電   | 技術        | 起》    | 原  |           |     |       | • •   |     |       |     | <br> | <br>. 1 | 2   |

|   | 3.3  | 微機    | 電   | 技術        | 介約    | 沼  |           |     |       | • •   |     |       |     | <br> | <br>. 1 | . 2 |

|   | 3.4  | 微機    | 電   | 技術        | 於石    | 汐製 | 程原        | 態用  |       | • • • |     |       |     | <br> | <br>. 1 | . 4 |

| 芽 | 第四章  | 章 厚   | 用房  | <b>制電</b> | 路言    | 設計 | <b></b> . |     |       |       |     |       |     | <br> | <br>. 1 | 6   |

|   | 4. 1 | 2.    | 4G  | CMO       | S 身   | 寸頻 | 開關        | 電   | 路之    | 之設    | 計.  |       |     | <br> | <br>. 1 | . 6 |

|   |      | 4.1.  | 1   | 電路        | 各設    | 計  | 目標        |     |       | • • • |     |       |     | <br> | <br>. 1 | . 6 |

|   |      | 4.1.  | 2   | 電路        | 各架    | 構言 | 2計        |     |       | • • • |     |       |     | <br> | <br>. 1 | . 7 |

|   | 4. 2 | 微機    | 電   | 製程        | 於智    | 電路 | 中之        | こ應  | 用.    | • • • |     |       |     | <br> | <br>. 2 | 2   |

|   | 4.3  | 2. 4G | Cl  | MOS       | 射步    | 頻開 | 關電        | 電路  | 製     | 作與    | 具模  | 擬.    |     | <br> | <br>. 2 | 26  |

|   |      | 4. 3. | 1 ' | 電路        | 特人    | 生模 | 擬         |     |       | • • • |     |       |     | <br> | <br>. 2 | 27  |

|   |      | 4. 3. | 2   | 變換        | 製和    | 呈參 | 數核        | 莫擬  |       | • • • |     |       |     | <br> | <br>    | 36  |

|     | 4. 3.    | 3 | 晶片 | 量 | 測 |     | <br>• | <br>• |   | • |   | • |     | • |   | • | <br>• | • | <br>  | . 4 | 16 |

|-----|----------|---|----|---|---|-----|-------|-------|---|---|---|---|-----|---|---|---|-------|---|-------|-----|----|

| 第五章 | <u> </u> | 結 | 論. |   |   | • • | <br>• | <br>• | • |   | • | • | • • | • | • |   | <br>• | • | <br>• | . 4 | 17 |

| 參考文 | 〔獻.      |   |    |   |   |     |       |       |   |   |   |   |     |   |   |   |       |   |       | . 5 | 50 |

# 圖 目 錄

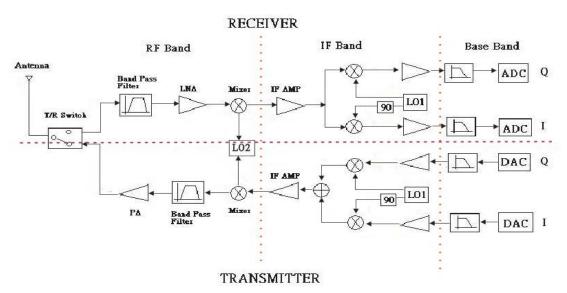

| 圖1.1     | 通訊系統架構示意圖1                 |

|----------|----------------------------|

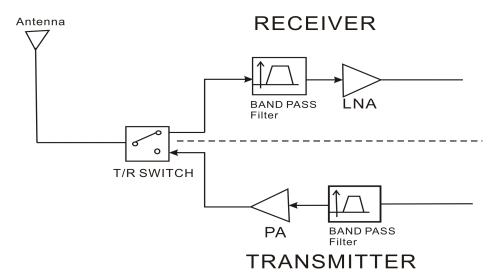

| 圖2.1.1   | 通訊系統架構概要圖7                 |

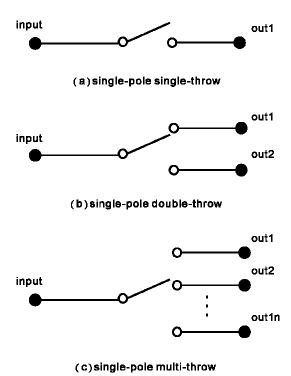

| 圖2.2.1   | 開關電路基本分類圖7                 |

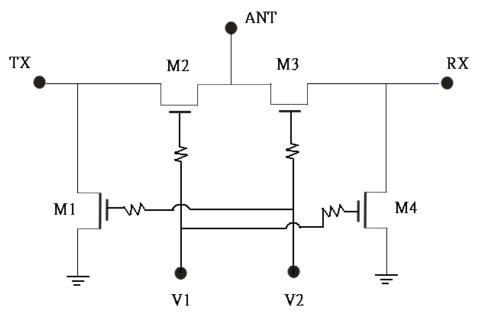

| 圖2.2.2   | FET開關電路示意圖9                |

| 圖2.2.3   | FET 開關電路TX側導通動作原理解析10      |

| 圖2.2.4   | FET 開關電路RX側導通動作原理解析10      |

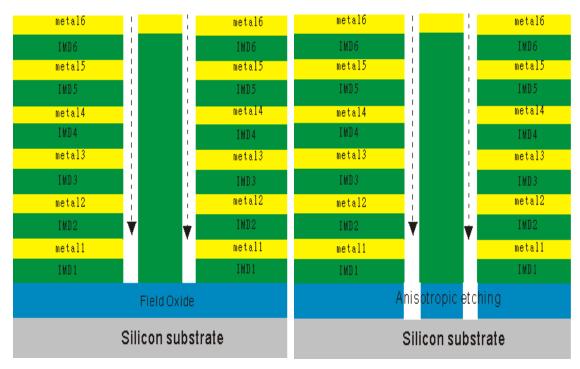

| 圖3.4.1   | 矽基板蝕刻類別示意圖15               |

| 圖4.1.1   | 電路設計流程圖17                  |

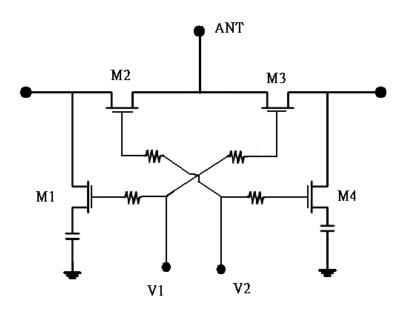

| 圖4.1.2   | 典型CMOS開關電路架構18             |

| 圖4.1.3   | 開關電路設計架構圖20                |

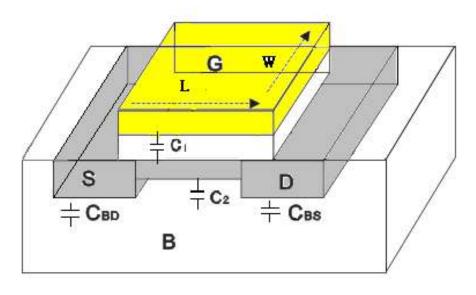

| 圖4.1.4   | MOS FET 寄生電容示意圖21          |

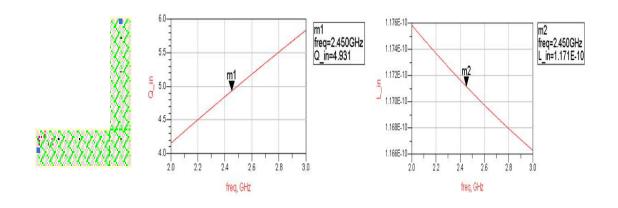

| 圖4.1.5   | 電感模擬與示意圖21                 |

| 圖4.2.1(a | a)(b)(c)CMOS製程進行矽基板蝕刻流程圖23 |

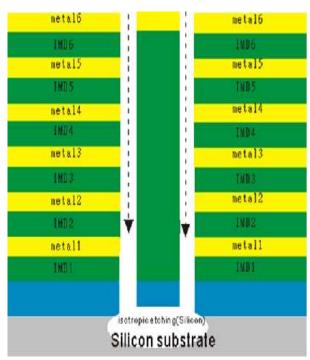

| 圖4.2.2   | 開關未使用MEMS後製程蝕刻插入損耗、功率承載    |

| 模擬結果[    | 圖25                        |

| 圖4.2.3   | 開關使用MEMS後製程蝕刻插入損耗、功率承載模    |

| 擬結果圖.    |                            |

| 圖4.3.1   | 開關電路設計布局圖26                |

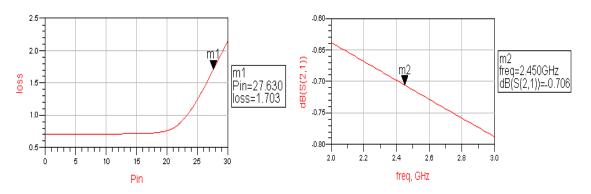

| 圖4.3.2  | 開關TX端功率承載模擬結果圖27        |

|---------|-------------------------|

| 圖4.3.3  | 開關TX端插入損耗模擬結果圖28        |

| 圖4.3.4  | 開關TX端反射損耗模擬結果圖29        |

| 圖4.3.5  | 開關TX端隔離度模擬結果圖30         |

| 圖4.3.6  | 開關RX端功率承載模擬結果圖31        |

| 圖4.3.7  | 開關RX端插入損耗模擬結果圖32        |

| 圖4.3.8  | 開關RX端反射損耗模擬結果圖33        |

| 圖4.3.9  | 開關RX端隔離度模擬結果圖34         |

| 圖4.3.10 | 開關TX端製程參數T/T插入損耗模擬結果圖36 |

| 圖4.3.11 | 開關TX端製程參數F/F插入損耗模擬結果圖37 |

| 圖4.3.12 | 開關TX端製程參數S/S插入損耗模擬結果圖38 |

| 圖4.3.13 | 開關TX端製程參數F/S插入損耗模擬結果圖39 |

| 圖4.3.14 | 開關TX端製程參數S/F插入損耗模擬結果圖40 |

| 圖4.3.15 | 開關RX端製程參數T/T插入損耗模擬結果圖41 |

| 圖4.3.16 | 開關RX端製程參數F/F插入損耗模擬結果圖42 |

| 圖4.3.17 | 開關RX端製程參數S/S插入損耗模擬結果圖43 |

| 圖4.3.18 | 開關RX端製程參數F/S插入損耗模擬結果圖44 |

| 圖4.3.19 | 開關RX端製程參數S/F插入損耗模擬結果圖45 |

| 圖4.3.20 | 電路量測考量示意圖46             |

# 表目錄

| 表一 | 過去文獻特性比較4   |

|----|-------------|

| 表二 | 模擬結果整理表35   |

| 表三 | 模擬結果與文獻比較48 |

## 第一章

### 緒論

今日數位通訊系統蓬勃發展,個人用無線通訊設備呈現大幅度的成長,為了讓通訊產品正使用上更輕巧方便,產品正朝著功能強、價格低、重量輕、體積小、耗電低的目標邁進,而系統單晶片(System on a Chip, SOC)正是能達到目標的途徑之一。隨著無線通訊產品不斷的推陳出新,推動整個無線通訊技術積極的創新。積體整合性高、功能強大、價格普及化、耗能小之相關的高頻元件和射頻電路、模組已成為發展無線通訊的首要目標。射頻積體電路位於無線通訊系統的前端如圖 1.1 所示。

圖 1.1 通訊系統架構示意圖

經由天線收發訊號,主要區分為接收部份和發射部份,系統藉由 射頻開關電路(RF Switch)做訊號接收或者發射,當系統切換接收訊 號時,射頻訊號經由天線接收到後,經由低雜訊放大器(LNA)、濾波器,藉著電壓控制振盪器(VCO)提供本地振盪訊號(LO Signal)與射頻訊號在混波器(Mixer)降頻至中頻訊號(IF Signal),最終輸入至訊號處理器並將其轉成所需的基頻資訊。如當系統切換到發射訊號時,基頻資訊調變至中頻訊號,再經過混波器升頻成射頻訊號,經過功率放大器(PA)、濾波器,經過開關電路,透過天線發射訊號。在無線通訊系統整合過程中,由於製程與模型準確度技術的提升,加上電路設計能力的進步,後端的數位與類比積體電路之間已有高度的整合。但是系統前端的高頻電路,在整合上卻出現瓶頸,如高頻功率放大器(PA)高頻開關(RF Switch)、高頻濾波器(RF filters)、共振器(resonator)等高頻電路與其他電路的整合度不高,至今這些高頻電路在通訊系統中仍然是以外加(off-chip)的方式運作。

有鑑於高頻開關電路的整合度不佳,因此本論文選擇研究設計高頻 CMOS 開關電路,希望能達到系統整合的目標。而過去在高頻 CMOS 開關的研究中,主要可分為兩個方向,一為 CMOS 之固態元件製作 RF Switch Circuit,為電子操作方式,另外是射頻微機電系統(RF MEMS)製作,是機械操作方式。

以 CMOS 固態電子元件製作的電路,其優點是元件開關速度快(約 幾十奈秒),但由於基板矽材料為導電材料,所以元件與基板間存在 寄生電容,使得訊號從這些寄生電容流失造成損耗(insertion loss) 過高。

而在過去文獻中對於 CMOS 元件所製作的高頻開關電路,在基板接大電阻或者 LC Tank[10]來增加基板的阻抗,又或者調整基板的參雜濃度提升的基板的阻抗[1]、或使用 DET 製程提升基板的阻值[2],等方式來降低訊號從基板流失而造成損耗過高,但以上這些方式如果是使用特殊製程,並不適用於目前的環境。另外,開關電路的功率承載(power handling)能力是另一個問題,低功率承載的原因其一是傳輸訊號(TX path)路徑無法承受高功率的訊號。另外是接收訊號路徑(RX path)無法承受高功率訊號在過去文獻指出,利用接收端路徑之開關利用元件串接方式可以將功率承載能力提高[13,14],不過這個做法會將接收路徑的損耗提高,造成系統接收能力降低,是此方法須考量的地方。過去文獻對於設計開關電路所呈現的特性及頻帶如表一所示:

| 表一:過去文獻特性比較 |                 |                      |         |                  |  |  |  |  |  |  |  |

|-------------|-----------------|----------------------|---------|------------------|--|--|--|--|--|--|--|

| Document    | parameter       |                      | process | technology       |  |  |  |  |  |  |  |

| [1]         | Frequency       | 5.8G                 | 0.18-μm | p- substrates    |  |  |  |  |  |  |  |

|             | P-1dB           | 17 dBm               | CMOS    |                  |  |  |  |  |  |  |  |

|             | IL              | 0.7dB(LS)0.9 dB(HS)  |         |                  |  |  |  |  |  |  |  |

|             | LS-HS Isolation | 30dB (LS)27.5 dB(HS) |         |                  |  |  |  |  |  |  |  |

| [2]         | Frequency       | 5G                   | 0.18-μm | DET Process      |  |  |  |  |  |  |  |

|             | IL              | 1.4 dB               | CMOS    |                  |  |  |  |  |  |  |  |

|             | Tx- Isolation   | 15 dB                |         |                  |  |  |  |  |  |  |  |

| [3]         | Frequency       | 15G                  | 0.13-μm | LC impedance     |  |  |  |  |  |  |  |

|             | P-1dB           | 21.5 dBm             | CMOS    |                  |  |  |  |  |  |  |  |

|             | IL              | 1.8 dB               |         |                  |  |  |  |  |  |  |  |

|             | Tx- Isolation   | 17.8 dB              |         |                  |  |  |  |  |  |  |  |

| [5]         | Frequency       | 900M                 | 0.5-μm  | VDB and VSB      |  |  |  |  |  |  |  |

|             | P-1dB           | 17 dBm               | CMOS    | levels increases |  |  |  |  |  |  |  |

|             | IL              | 0.73 dB              |         |                  |  |  |  |  |  |  |  |

|             | Tx- Isolation   | 41 dB                |         |                  |  |  |  |  |  |  |  |

另外近幾年來,微機電系統(Micro-electro-mechanical systems, MEMS)技術隨著製程不斷演進與多元化整合,目前已逐漸在電機電子領域占有一席之地。而利用MEMS製作的開關電路[17]有低的損耗,在文獻也指出其功率承載也有很好的表現,不過要操作MEMS開關電路,需要很大的操作電壓(30~80 volts),是一般通訊系統沒辦法提供如此高的偏壓。另一方面,MEMS開關電路是屬於機械式開關,其開關時間與電子式開闢相比,顯得非常慢(約300 us),因此MEMS開關電路尚還不能滿足系統上的應用。因此,本論文將過去高頻 CMOS

開關電路再進一步改善。電路架構上是承接過去的架構,使用高阻抗之基極電阻,降低損耗。也將RX元件串/並連接,提高功率承載。並且更進一步借由微機電製程,將電路之傳輸線懸浮,降低訊號在傳送中之損耗,並且,在電路之輸入及輸出做阻抗匹配,降低因阻抗不匹配所增加的損耗。從模擬結果可得到,藉由傳輸線懸浮以及阻抗匹配,可改善23.7%之損耗特性。

本論文內容大致可分為五個章節:

第一章為緒論,主要介紹高頻 CMOS 開關過去發展與目前現況,並說明使用何種方法改善高頻 CMOS 開關電路的特性。

第二章為說明高頻 CMOS 開關電路的功能與原理。

第三章為說明使用 MEMS 製程可為高頻 CMOS 開關電路所帶來的幫助與 MEMS 製程的介紹。

第四章為電路設計說明與電路的布局與模擬結果。

第五章為本論文的結論,對於此次設計的結果做一個概括性的討論。

## 第二章

## 開關電路原理說明

本章主要對於開關電路的功能類別、電路工作時所需要了解的特 性以及電路工作時運行的動作原理加以介紹。

#### 2.1 開闢電路功能概述

高頻CMOS 開關電路[1,2,3]被用於許多的通訊系統上,而它通常處於通訊系統中如圖2.1.1所示的位置,用來當接收訊號亦或者傳輸訊號時經過的路徑。而開關的設計通常使用的元件為二極體或是FET等電子元件,在開關電路中通常以插入損耗(insertion loss)、功率承載力(power handling)、隔離度(isolation)等特性為觀察的重點。其中插入損耗代表當開關電路開啟時,訊號從輸入端傳輸至輸出端的損耗大小。隔離度則是開關電路關閉時,訊號由輸入端流至輸出端的多寡,隔離度越大則表示TX端與RX端之間訊號影響程度就越低,power handling指的是切換開關能夠不影響電路特性的前提下,所能承受的最大功率輸入能力。

圖 2.1.1 通訊系統架構概要圖

#### 2.2 開關設計原理與分類

若以路徑切換的數目來區分開關電路,大致可以分為:

single-pole single-throw(SPST)、 single-pole double-throw

(SPDT)和 single-pole multi-throw 等類型。如圖 2.2.1(a)(b)(c)

所示

圖 2.2.1 開關電路基本分類圖

而以CMOS開關電路所使用的電子元件作為區分的準則說,則大致可以分為使用PIN Diode 切換開關、FET 切換開關,並在以下分別作為介紹[4]:

#### PIN Diode 開關電路

PIN diode 主要應用於高頻或微波電路切換開關中,可以視為一個以電流控制的電阻。PIN diode主要操作在高頻,導通時會有低插入損耗與高功率承載,所以PIN diode通常用於高功率切換開關,其缺點為要使PIN diode 導通需要較高的控制電壓,因此需要額外設計控制驅動電路。而PIN diode導通電流通常較大,並不適合用於所有的通訊系統。

#### FET開關電路

FET開關電路可以分為使用GaAs MESFET或MOS FET,電路示意圖如圖2.2.2所示[5],而其中GaAs MESFET,具有寬頻、低插入損耗與高功率開關等特性。GaAs MESFET 開關電路為一個由電壓控制的電阻。而為了增加其隔離度,同樣可以串聯多個MESFET 或加入並聯架構來改善電路特性。而使用MOS FET 的開關電路與GaAs MESFET 相同,為一個以電壓控制的電阻。但是MOS FET 的功率承載力、插入損耗等特性並不如使用GaAs MESFET所製作的開關電路。而此為MOS FET在電路特性上所面臨的挑戰。

圖2.2.2 FET開關電路示意圖

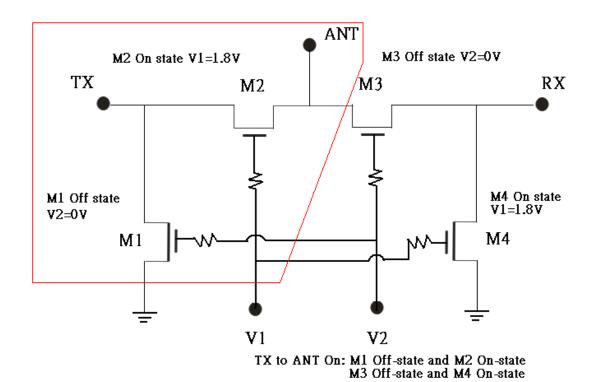

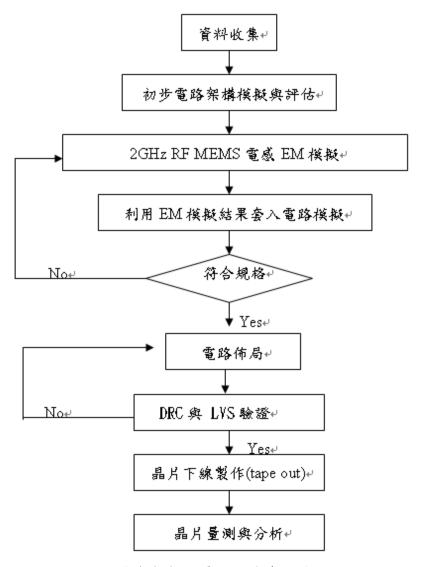

分析T/R 開關電路設計動作原理可以分別由TX端與RX端兩側來解釋,TX端電路動作分析如圖2.2.3所示,當TX側為導通的狀態驅動電壓設定給予1.8V時,TX側所存在的MOS FET相當於低阻值電阻可以讓訊號以低損耗的狀態通過與此同時在RX側MOS FET則為關閉的狀態,用來阻絕訊號不使訊號通過。若分析RX端的動作則如圖2.2.4所示,當RX端為導通的狀態時,則T/R開關電路中MOS FET的動作行為與TX端導通時原理相同。為RX側所存在的MOS FET相當於低阻值電阻可以讓訊號以低損耗的狀態通過與此同時在TX側MOS FET則為關閉的狀態,用來阻絕訊號不使訊號通過。

圖2.2.3 FET 開關電路TX側導通動作原理解析

圖2.2.4 FET 開關電路RX側導通動作原理解析

## 第三章

### 微機電技術介紹

本章主要對於微機電系統(Micro-electro-mechanical systems, MEMS)的背景與技術加以介紹。並說明微機電系統於此次設計的作用。 3.1 微機電作用說明

此次使用 TSMC 0.18 CMOS 製程進行,而在電路設計中需要使用電感元件,但由於矽製程中使用高摻雜低電阻係數的基底,所以基底的損耗會比砷化鎵等特性較佳的製程來的多,所以矽製程中的電感元件普遍Q值不佳。其原因為當金屬導線的電流在金屬線中流動,產生一個向上的磁場時,此時會在基底感應出一個流動方向與其相反的電流 用來反抗外來的磁場變化,而這個感應電流在基底中流動會造成損耗,另外金屬和基底之間存在的寄生電容,會把在基底流動的電流耦合到金屬線上,並把基底的雜訊帶到金屬線,造成訊號的損失。所以使用 MEMS 製程,即後 CMOS 製程(post-CMOS process)蝕刻矽基板的方式,避免基底的雜訊帶到金屬線而影響到電路的特性,並且配合CMOS 開關電路使用,進而降低插入損耗(insertion loss)的損失[6,7,8]。

#### 3.2 微機電技術起源

微機電系統(Micro-electro-mechanical systems, MEMS)在歐洲被稱為微系統科技(micro system technology)。起源於1959年美國物理學年會上由費曼博士發表"There plenty of room at the bottom"的專題演講中,提到把機器微型化的概念,進而從此展開微機電系統的發展,如今微機電的發展已逐漸由學術研究走入產業界,進而衍生出許多商品,而其涵蓋的範圍包含光學電子電機機械通訊材料物理化學等多種知識與技術[9]。

#### 3.3微機電技術介紹

雖然1959 年費曼博士於美國物理學年會上的專題演講中首先提出了機器微型化的概念。但真正促使微機電技術蓬勃發展的推手還是由於半導體製程技術的日驅成熟,使得製作微機電元件之可能性大大提升。所以標準半導體製程技術與微機電製程技術常常密不可分,如薄膜沉積、微影與蝕刻技術,可是微機電系統的發展雖然是搭著半導體製程設備與技術的便車,但由於性能與結構上的要求已不同於積體電路,所以也逐步發展出不同的製造技術。與標準的積體電路結構相比,微機電元件的結構特徵有:三維結構、高深寬比、可動結構與多元性材料。

#### (1)三維結構

積體電路基本上是一個平面結構,但微機電元件的幾何形狀比較複雜,配合晶片結合技術,常有微柱、微孔、微腔室及微溝等立體結構, 再搭配立體微接頭,可構成多變的三維結構。

#### (2)高深寬比

為了增加強度或感測及驅動量,微元件的厚度常要求很高,可能是數或到數百微米,甚至更厚,但微結構中的微孔或間距可能只要數微米,側壁垂直度要好,所以發展出厚膜光阻、深蝕刻、同步輻射X光光刻等技術。

#### (3)可動結構

微機電元件常可見到立體或懸浮式的微結構,以容許微結構變形或運動,所以掏空微結構材料的犧牲層技術、背面蝕刻技術、連接懸浮結構而行成立體結構的微鉸鏈技術,及避免懸浮結構與下層基底沾黏的技術,都是微機電製程中特有的技術。也由於微機電元件長有中空或懸浮式結構,微元件及微系統所需的封裝技術,也就常不同於電子元件已發展相當成熟的封裝技術,目前仍處於發展中的階段。

#### (4)多元性材料

早年微機電元件的結構中多是用矽基材料,如單晶矽、複晶矽、氮化矽或二氧化矽等,再搭配一些金屬,如鋁,因為這些可用標準半導體製程製作,但隨著微機電元件的多樣化,也越來越常用到各式金屬及高分子材料,甚至用到所謂之智慧型材料,如壓電、磁性材料及形狀記憶合金,這些就不是目前標準半導體製程所能提供,所以非矽材料的微加工製程技術在微機電製程日漸重要,如微放電加工及深刻模造術中的精密電鑄及微成形技術。

#### 3.4 微機電技術於矽製程應用

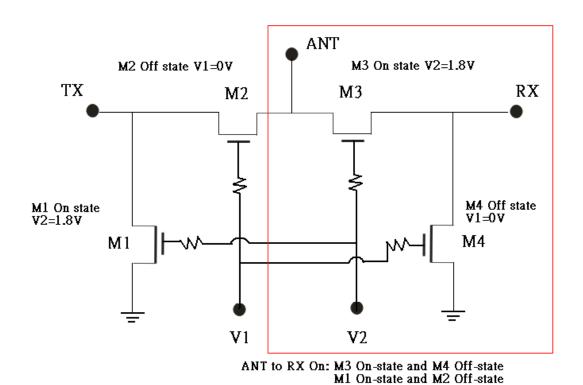

微機電技術通常在矽晶圓或者在矽晶片上使用,利用沉積曝光顯影蝕刻等方式依序將所需之微機械結構定義出來,而早期運用之微結構形成機制多半在於利用矽晶片材質的非等向性晶格方向和各不同材質間的蝕刻選擇比來達成微元件裝置。而在微機電製造技術中有一技術種類為體型微加工,這種技術即為對基板進行等向及非等向性乾/濕蝕刻,進而把基板做不同程度的使用,而基材材料為單晶矽及砷化鎵等半導體材料。若以蝕刻矽基板為例來介紹該技術則可以分為乾式蝕刻及濕式蝕刻兩類。濕式蝕刻是使用液態化學溶劑對矽基板進行蝕刻,而乾式蝕刻是使用電漿(高能量的離子氣體)或者是氣相蝕刻劑來對矽基板進行蝕刻。而蝕刻時又可以依照最後形成的微結構輪廓來

分類。而濕式蝕刻的速率與蝕刻基體的晶格方向有關,而乾式蝕刻在 蝕刻速率上與晶格方向無關,若在所有方向的蝕刻速率不同的話,則 可稱此蝕刻為非等向性(anisotropic)蝕刻,若蝕刻速度在任一方向 的速率相同,則可稱之為等向性(isotropic)蝕刻其蝕刻示意圖,如 圖 3.4.1 所示。

圖 3.4.1 矽基板蝕刻類別示意圖

# 第四章 開關電路設計

本章節將對於設計時高頻 CMOS 開關電路時的目標、考量及電路 完成後的模擬結果加以說明。

#### 4.1 2.4G CMOS 射頻開關電路之設計

#### 4.1.1 電路設計目標

電路的設計目標為使用 TSMC 0.18 µm CMOS 製程,製作一個驅動電壓為 1.8V 的 2.4GHz CMOS 之射頻開關電路,其使用模擬軟體為 ADS (Advanced Design System),設計目標為使該射頻開關電路[10,11,12]能擁有高功率承載,低損耗,高隔離度的效能,要實現以上的考量,必須要在架構上選擇出最適合此電路的 MOS FET 尺寸,以達到設計電路架構時所需要的最低損耗及最高的功率承載能力,為了使電路擁有最佳的功率承載能力與最低的損耗,在此處將 MOS FET 以串聯及並聯(series/shunt)並用的形式來提升電路功率承載能力,以及降低電路的損耗。

#### 4.1.2 電路架構設計

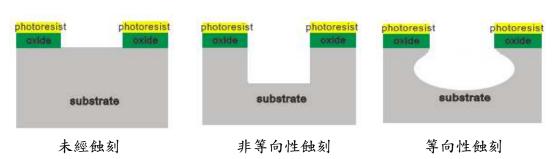

在設計 CMOS 射頻開關電路時,圖 4.1.1 為設計流程圖,設計步驟以設計流程圖為參考,避免設計時思緒混亂才可以更有效率的完成電路設計,而圖 4.1.2 為開關電路中最典型的架構。

圖 4.1.1 電路設計流程圖

圖 4.1.2 典型 CMOS 開關電路架構

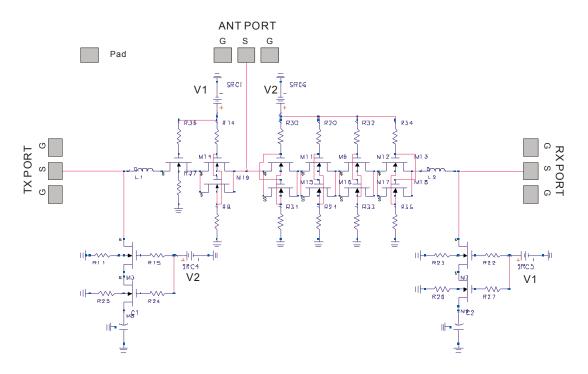

圖 4.1.3 為此次電路架構圖,電路設計說明可以分為以下三個部分:

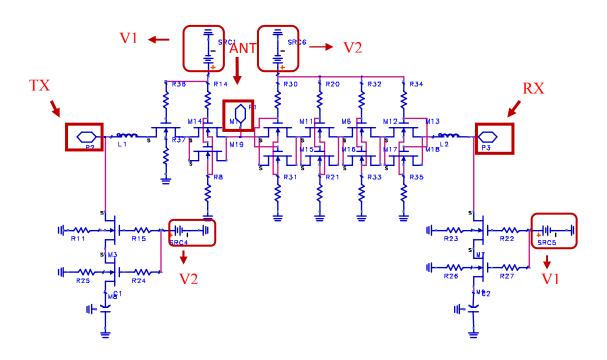

TX的部份:在TX端我們主要考慮電路功率承載能力以及訊號損失這兩個問題,使用FET 串接的方式提升功率承載力(power handling),而串接顆數為兩顆,並且使用FET 並接降低插入損耗(insertion loss),利用此設計方式考量,電路模擬結果是否在電路設計規格的承受範圍之內。由圖 4.1.3 可發現TX端串接部分(series)採用通道長度  $L=0.18\,\mu$ m,寬度  $W=8\,\mu$ m,figer 數=64 的 FET 並使用並一串的方式連接,TX端並接部分(shunt)使用通道長度 L=0.5 Lum,寬度 W=1.5 Lum,finger 數=20 的 FET 連接,並在 MOS FET 基板上接 50 R  $\Omega$  大電阻,增加基板的阻抗,降低訊號從基板流失而造成損耗過高。

RX 的部分: 在 RX 端串接 FET 的方式來增加功率承載能力,其串接顆數為四顆,用來提升 TX 的功率承載力(power handling)[13,14]

同時使 FET 並接降低 RX 的插入損耗(insertion loss),藉由這種方式提升電路特性以符合電路設計時所設定的規格。由圖 4.1.3 可發現 RX 端串接部分使用通道長度  $L=0.18\,\mu$  m,通道寬度  $W=8\,\mu$  m,figer 數 =64 的 MOS FET 並使用並一串的方式連接,RX 端並接部分(shunt)使用通道長度 L=0.5 um,寬度 W=1.5 um,finger 數=20 的串接,並在 FET 基板上接 50 k  $\Omega$  大電阻,增加基板的阻抗,降低訊號從基板流失而造成損耗過高。

MATCHING 部分: MATCHING 部分在這個開闢電路中是一個重要的設計概念,由於使用傳統平面螺旋電感時,特性不佳,無法有效使用於 MATCHING 部分,提升電路特性,所以利用微帶線電感效應製作特定感值的電感,取代平面螺旋電感,提升電感特性使其與圖 4.1.4 中所表示的寄生電容做 MATCHING 減少電路的 return loss 與訊號的損失,以進一步完善電路的設計,提升電路特性。微帶線電感是根據微帶線電感效應與後 CMOS 製程使用 ADS(Advanced Design System)\_Momentum 所模擬一個 L值=171 pH,Q=4.931 的微帶線電感,電感模擬與示意圖如圖 4.1.5 所示。其中電感 Q值[15]可以表示為:

$$Q = \frac{2\pi fL}{R} \tag{1}$$

f=操作頻率

L=是電感值

#### R=為寄生在電感之電阻值。

圖 4.1.3 開關電路設計架構圖

利用上述方式設計電路之後,使用 ADS (Advanced Design System)

模擬電路結果可以得到下列模擬數值:

TX: Power handling=27.390dBm

Insertion loss=0.538dB

Isolation=-23.070dB

Return loss S11=-28.226dB, S22=-26.391dB

RX: Power handling=20.210dBm

Insertion loss=0.630 dB

Isolation=-19.948dB

Return loss S33=-25.986dB, S22=-23.967dB

圖 4.1.4 MOS FET 寄生電容示意圖

圖 4.1.5 電感模擬與示意圖

#### 4.2 微機電製程於電路中之應用

由圖4.1.4中可得知在MOS FET中存在寄生電容,所以在設計電路時可以利用阻抗匹配的觀念在電路中加入一個電感元件與寄生電容匹配,藉此減少電路的插入損耗與反射損耗提升電路的特性,電感元件所使用的金屬層為metal5與metal6,使用這兩層金屬製作電感元件可以使電感元件的特性較佳,而且電路中進行矽基板蝕刻的傳輸線也是使用metal5與metal6來製作,降低傳輸線的損耗,這裡使用ADS(Advanced Design System)\_Momentum模擬 MEMS後製程進行矽基板蝕刻的方法如圖4.2.1(a)(b)(c),其蝕刻流程如圖(a)至(c),進行矽基板蝕刻的方式可以減少電流耦合到金屬導線上時所帶來的影響,進而提升電感的特性,可以使電感更有效的與MOS FET中的寄生電容作匹配的動作,而提升整體電路的效果。

圖4.2.1(a)為MEM製程在0.18μm CMOS 製程進行矽基板蝕刻流程圖

圖4.2.1(b)為MEM製程在0.18μm CMOS 製程進行矽基板蝕刻流程圖

圖4.2.1(c)為MEM製程在0.18μm CMOS製程進行矽基板蝕刻流程圖

使用MEMS後製程,進行矽基板蝕刻可以減少電流耦合到金屬導線 上所帶來的影響,有鑒於此,在此設計中,對於幾個主要會造成損耗 的傳輸線使用MEMS製程,利用蝕刻的方式將傳輸線下方的矽基材蝕刻 去除,使傳輸線損耗減少,藉此減少信號的損耗,以提昇整體電路的 特性,並且使用ADS(Advanced Design System) Momentum模擬[16] 電路特性,圖4.2.2是電路中傳輸線未做MEMS後製程處理之前的ADS (Advanced Design System) Momentum電磁模擬TX端的模擬結果,此 時電路TX端Pin功率承載力為27.630dBm及insertion loss為 0.706dB。 圖 4.2.3 為 電路 中 傳 輸 線 做 MEMS 後 製 程 處 理 之 後 的 ADS(Advanced Design System) Momentum電磁模擬TX端的模擬結果此 時電路TX端Pin功率承載為27.400dB,及insertion loss為0.538dB。 由以上兩圖的模擬比較可以發現利用蝕刻的方式將傳輸線下方的矽 基材蝕刻去除,確實可以使傳輸線損耗減少進而提升電路的特性,減 少訊號23.7%的損失。

圖4.2.2 模擬傳輸線與微帶線電感未做MEMS後製程之前開關電路 2.45G特性 TX Pin=27.630dBm Insertion loss=0.706dB

圖 4.2.3 模擬傳輸線與微帶線電感做 MEMS 後製程之後開關電路 2.45G 特性 TX Pin=27.400dBm Insertion loss=0.538dB

## 4.3 2.4G CMOS 射頻開關電路製作與模擬

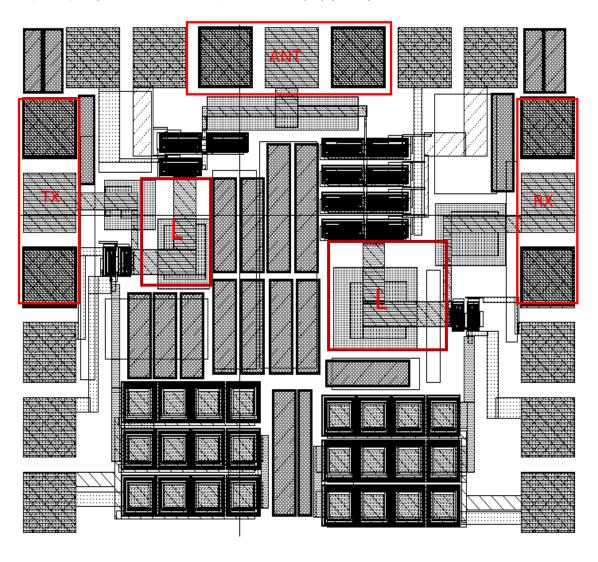

電路設計完成時,對於所設計的電路會使用 virtuoso Layout 軟體進行電路布局,電路布局圖如圖 4.3.1 所示。Layout 圖中上方紅框為電路設計中 ANTENNA 所在的位置,左側紅框為電路中 TX 端訊號進入的位置,反之,右側紅框 RX 端所在位置。

圖 4.3.1 開關電路設計布局圖

#### 4.3.1 電路特性模擬

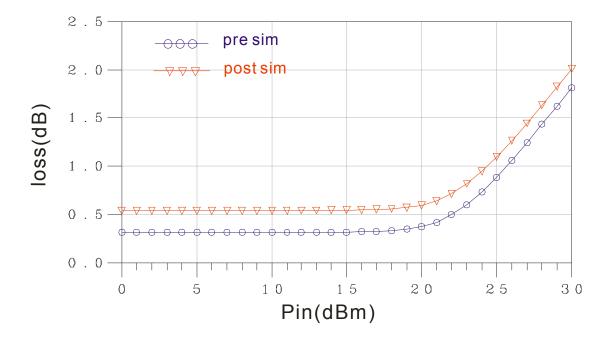

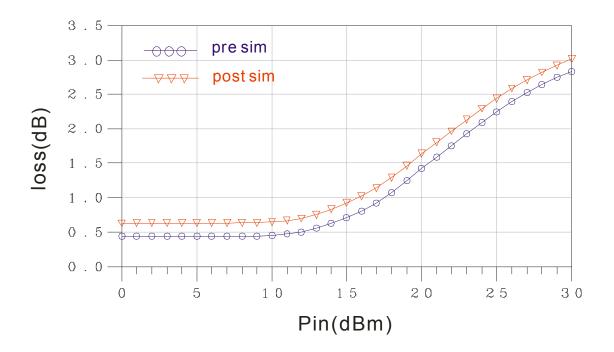

電路模擬時主要可以分為不考慮傳輸線效應時的模擬結果,在此稱之為 Pre-sim 及考慮傳輸線效應對於整體 Layout 使用 ADS\_Momentum 電磁模擬的模擬結果,稱之為 Post-sim,並對兩種模擬做比較,圖 4.3.2 為電路 TX 端功率承載 Pin 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的功率承載 Pin 為 27.280dBm,考慮傳輸線效應時 TX 端的功率承載 Pin 為 27.280dBm,考慮傳輸線效應時 TX 端的功率承載 Pin 為 27.390dBm。其中圖 4.3.2~ 圖 4.3.9 模擬結果圖製程參數皆選用 T/T。

圖 4.3.2 未考慮傳輸線寄生效應模擬 2.45G TX 的功率承載 Pin 為 27.280dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX 的功率承載 Pin 為 27.390dB。

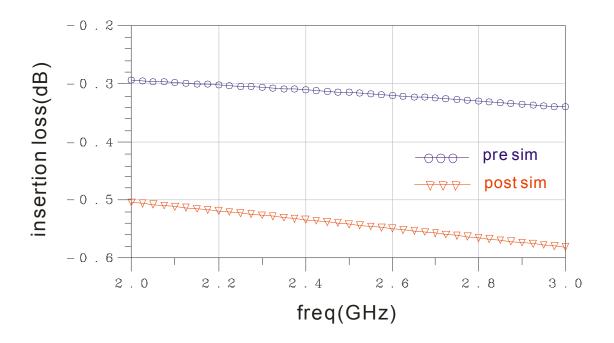

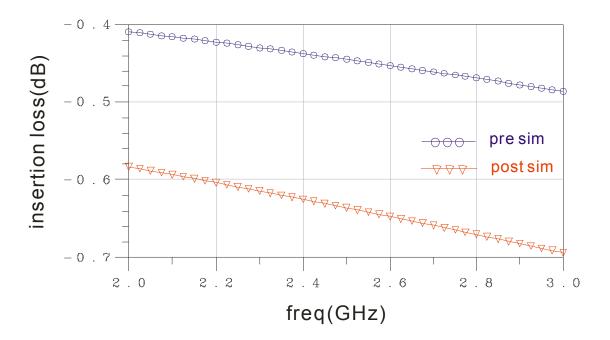

圖 4.3.3 為電路 TX 端 insertion loss 的比較結果。其中不考慮 傳輸線效應時的模擬結果 TX 端的 insertion loss 為 0.313dB,考慮 傳輸線效應時 TX 端的 insertion loss 為 0.538dB

圖 4.3.3 未考慮傳輸線寄生效應模擬 2.45G TX insertion loss 為 0.313dB。 考慮傳輸線寄生效應使用電磁模擬 2.45G TX insertion loss 為 0.538dB。

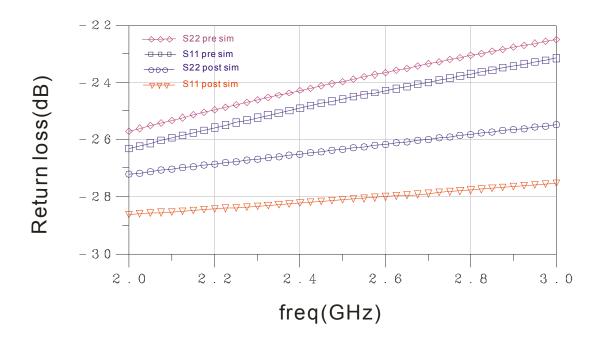

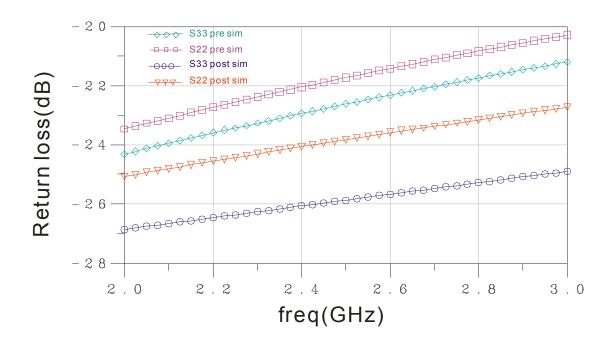

圖 4.3.4 為電路 TX 端 return loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 return loss S11=-24.756dB S22=-24.124dB , 考慮傳輸線效應時 TX 端的 return loss S11=-28.226dB S22=-26.391dB。

圖 4.3.4 未考慮傳輸線寄生效應模擬 2.45G TX return loss 分別為 S11=-24.756dB S22=-24.124dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX return loss 分別為 S11=-28.226dB, S22=-26.391dB。

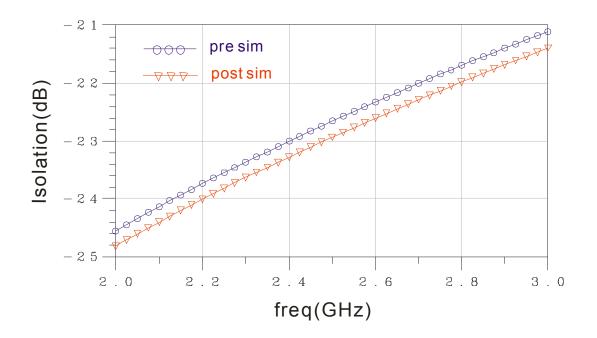

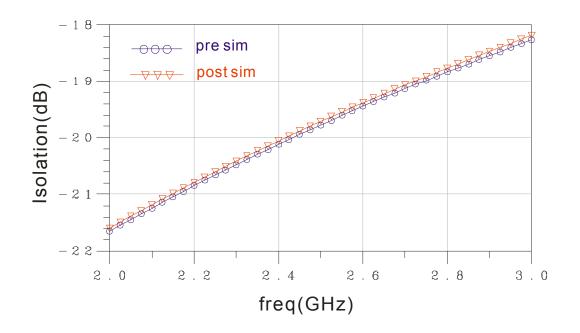

圖 4.3.5 為電路 TX 端 isolation 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 isolation 為-22.826dB,考慮傳輸線效應時 TX 端的 isolation 為-23.070dB。

圖 4.3.5 未考慮傳輸線寄生效應模擬 2.45G TX isolation 為-22.826dB。 考慮傳輸線寄生效應使用電磁模擬 2.45G TX isolation 為-23.070dB。

圖 4.3.6 為電路 RX 端功率承載 Pin 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的功率承載 Pin 為 20.220dBm,考慮傳輸線效應時 RX 端的功率承載 Pin 為 20.210dBm

圖 4.3.6 未考慮傳輸線寄生效應模擬 2.45G RX 的功率承載 Pin 為 20.220dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX 的功率承載 Pin 為 20.210dB。

圖 4.3.7 為電路 RX 端 insertion loss 的比較結果。其中不考慮 傳輸線效應時的模擬結果 RX 端的 insertion loss 為 0.441dB,考慮 傳輸線效應時 TX 端的 insertion loss 為 0.630dB。

圖 4.3.7 未考慮傳輸線寄生效應模擬 2.45G RX insertion loss 為 0.441dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX insertion loss 為 0.630dB。

圖 4.3.8 為電路 RX 端 return loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 return loss S33=-22.770dB S22=-21.882dB , 考慮傳輸線效應時 RX 端的 return loss S33=-25.986Db S22=-23.967dB。

圖 4.3.8 未考慮傳輸線寄生效應模擬 2.45G RX return loss 分別為 S33=-22.770dB, S22=-21.882dB。考慮傳輸線寄生效應使用電磁模擬 2.45GRX return loss 分別為 S33=-25.986dB, S22=-23.967dB。

圖 4.3.9 為電路 RX 端 isolation 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 isolation 為-19.948dB,考慮傳輸線效應時 RX 端的 isolation 為-19.948dB。

圖 4.3.9 未考慮傳輸線寄生效應模擬 2.45GRX isolation 為 -19.948dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX isolation 為 -19.948dB。

電路模擬結果整理,如表二所示,其中 Pre-sim 代表電路模擬時,並未使用 ADS\_Momentum 模擬 Layout 圖中金屬傳輸線時的模擬結果。Post-sim 即為已使 ADS\_Momentum 模擬 Layout 圖中金屬傳輸線時的模擬結果,為布局時所呈現的模擬結果。

| 表二:模擬結果整理       |             |             |             |             |  |  |  |  |

|-----------------|-------------|-------------|-------------|-------------|--|--|--|--|

| Specification   | TX          |             | RX          |             |  |  |  |  |

|                 | Pre-sim     | Post-sim    | Pre-sim     | Post-sim    |  |  |  |  |

| Freq(GHz)       | 2.45G       | 2.45G       | 2.45G       | 2.45G       |  |  |  |  |

| VDD             | 1.8V        | 1.8V        | 1.8V        | 1.8V        |  |  |  |  |

| Insertion       | 0.313       | 0.538       | 0.441       | 0.630       |  |  |  |  |

| loss(dB)        |             |             |             |             |  |  |  |  |

| Pin-1dB(dBm)    | 27.280      | 27.390      | 20.220      | 20.210      |  |  |  |  |

| Isolation(dB)   | -22.826     | -23.070     | -19.948     | -19.948     |  |  |  |  |

| Return loss(dB) | S11=-24.756 | S11=-28.226 | S33=-22.770 | S33=-25.986 |  |  |  |  |

| Return loss(dB) | S22=-24.124 | S22=-26.391 | S22=-21.882 | S22=-23.967 |  |  |  |  |

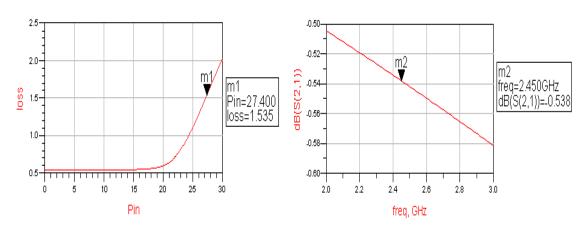

### 4.3.2 變換製程參數模擬

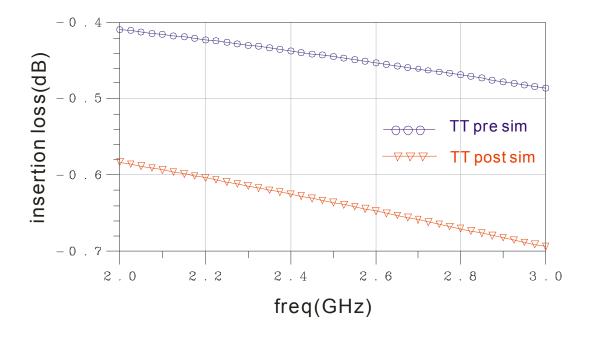

圖 4.3.10 為電路模擬時製程參數選用 T/T , TX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 insertion loss 為 0.313dB , 考慮傳輸線效應時 TX 端的 insertion loss 為 0.538dB。

圖 4.3.10 未考慮傳輸線寄生效應模擬 2.45G TX tt insertion loss 為 0.313dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX tt insertion loss 為 0.538dB。

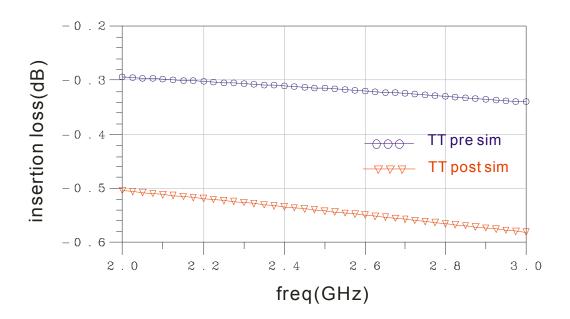

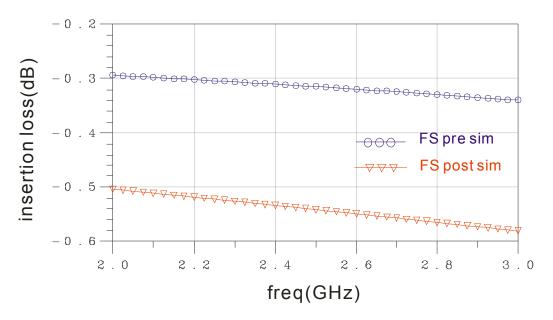

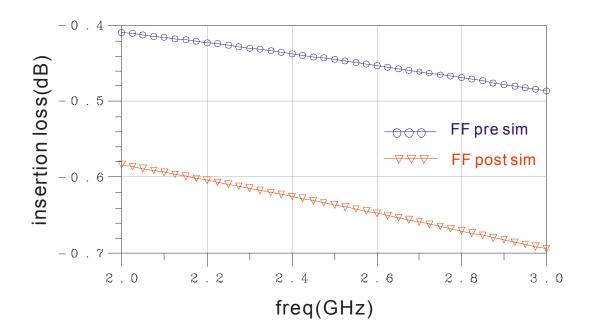

圖 4.3.11 為電路模擬時製程參數選用 F/F , TX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 insertion loss 為 0.313dB , 考慮傳輸線效應時 TX 端的 insertion loss 為 0.538dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.11 未考慮傳輸線寄生效應模擬 2.45G TX ff insertion loss 為 0.313dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX ff insertion loss 為 0.538dB。

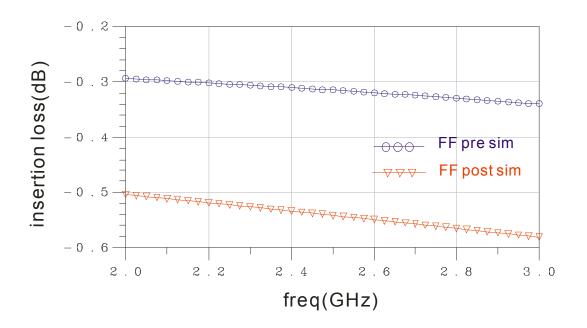

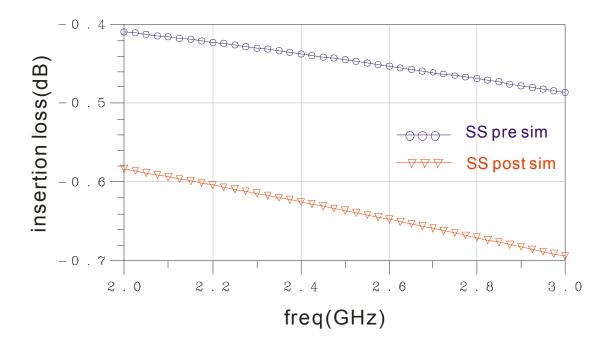

圖 4.3.12 為電路模擬時製程參數選用 S/S , TX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 insertion loss 為 0.313dB , 考慮傳輸線效應時 TX 端的 insertion loss 為 0.538dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.12 未考慮傳輸線寄生效應模擬 2.45G TX ss insertion loss 為 0.313dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX ss insertion loss 為 0.538dB。

圖 4.3.13 為電路模擬時製程參數選用 F/S , TX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 insertion loss 為 0.313dB , 考慮傳輸線效應時 TX 端的 insertion loss 為 0.538dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.13 未考慮傳輸線寄生效應模擬 2.45G TX fs insertion loss 為 0.313dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX fs insertion loss 為 0.538dB。

圖 4.3.14 為電路模擬時製程參數選用 S/F , TX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 TX 端的 insertion loss 為 0.313dB , 考慮傳輸線效應時 TX 端的 insertion loss 為 0.538dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.14 未考慮傳輸線寄生效應模擬 2.45G TX sf insertion loss 為 0.313dB。考慮傳輸線寄生效應使用電磁模擬 2.45G TX sf insertion loss 為 0.538dB。

圖 4.3.15 為電路模擬時製程參數選用 T/T , RX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 insertion loss 為 0.441dB,考慮傳輸線效應時 RX 端的 insertion loss 為 0.630dB。

圖 4.3.15 未考慮傳輸線寄生效應模擬 2.45G RX tt insertion loss 為 0.441dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX tt insertion loss 為 0.630dB。

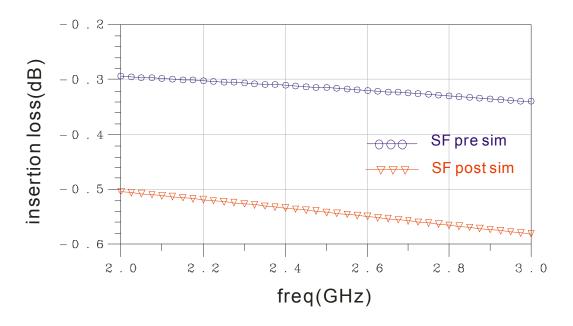

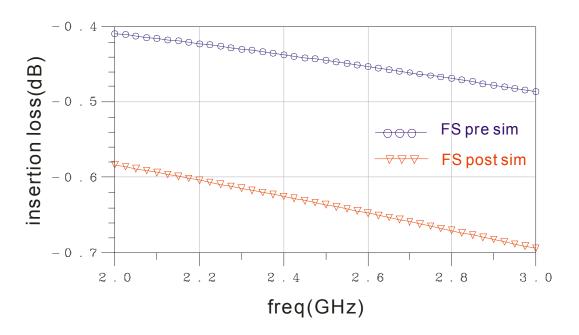

圖 4.3.16 為電路模擬時製程參數選用 F/F ,RX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 insertion loss 為 0.441dB,考慮傳輸線效應時 RX 端的 insertion loss 為 0.630dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.16 未考慮傳輸線寄生效應模擬 2.45G RX ff insertion loss 為 0.441dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX ff insertion loss 為 0.630dB

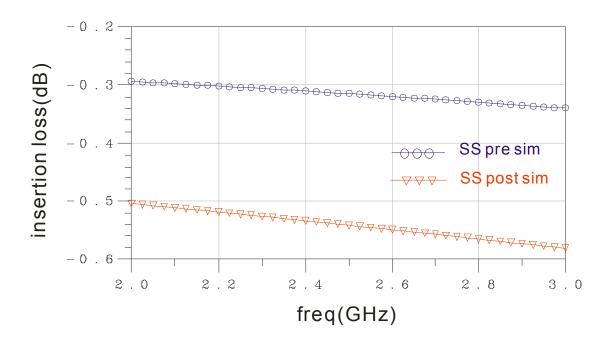

圖 4.3.17 為電路模擬時製程參數選用 S/S , RX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 insertion loss 為 0.441dB,考慮傳輸線效應時 RX 端的 insertion loss 為 0.630dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.17 未考慮傳輸線寄生效應模擬 2.45G RX ss insertion loss 為 0.441dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX ss insertion loss 為 0.630dB。

圖 4.3.18 為電路模擬時製程參數選用 F/S , RX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 insertion loss 為 0.441dB,考慮傳輸線效應時 RX 端的 insertion loss 為 0.630dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.18 未考慮傳輸線寄生效應模擬 2.45G RX fs insertion loss 為 0.441dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX fs insertion loss 為 0.630dB。

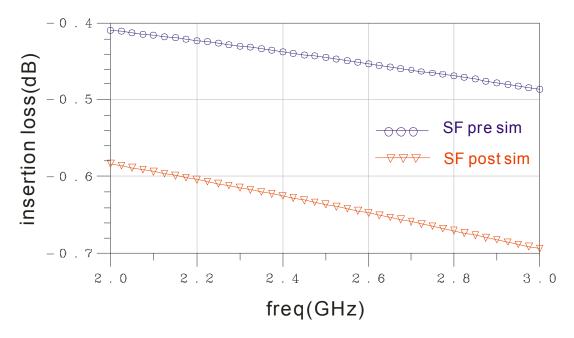

圖 4.3.19 為電路模擬時製程參數選用 S/F , RX 端 insertion loss 的比較結果。其中不考慮傳輸線效應時的模擬結果 RX 端的 insertion loss 為 0.441dB,考慮傳輸線效應時 RX 端的 insertion loss 為 0.630dB。與製程參數 T/T 模擬結果比較並無差異。

圖 4.3.19 未考慮傳輸線寄生效應模擬 2.45G RX sf insertion loss 為 0.441dB。考慮傳輸線寄生效應使用電磁模擬 2.45G RX sf insertion loss 為 0.630dB。

由以上圖 4.3.10~圖 4.3.19 的模擬結果可以得知,在切換製程 參數的影響下,對於模擬結果而言並無明顯的影響,模擬結果在不同 製程參數下所呈現的數據,均為相同。

### 4.3.3 晶片量測

此電路是預計使用on-wafer 方式量測收發切換開關,利用下針量測,使用的是RF探針,並且配合實驗室的網路分析儀加以量測。另外利用DC探針下針方式提供1.8V驅動電壓,量測2至3G頻段所呈現的S參數變化及電路的P-1dB點並參考2.45G量測點所呈現之參數是否與模擬結果相同。圖4.3.20為此次電路量測考量示意圖。

圖4.3.20 電路量測考量示意圖

# 第五章 結論

本文主要對於使用 TSMC 0.18 CMOS 製程、驅動電壓 1.8V、工作頻率 2.4GHz 的 CMOS 開關電路進行研究與設計,論文中主要介紹微機電技術的使用,以及開關電路的種類和動作原理,並且根據這些技術與原理,設計此次電路的架構。在電路中加入電感元件與 MOS FET中的寄生電容作匹配阻抗,減少插入損耗。但由於傳統電路設計中MOS FET開關電路的插入損耗、功率承載的能力相較於利用異質接面元件(Hetero junction device),如 pHemt, GaAs 所製作之開關電路相比,仍有差距,因此對於電路中的電感元件及傳輸線,使用微機電技術刻將傳輸線下方的矽基材蝕刻去除,確實可使傳輸線損耗減少進而提升電路的特性,從之前的模擬結果發現此做法可以使訊號減少23.7%的損失。而 TX 端功率承載率可以維持在 27.390dBm。並與參考文獻之特性做比較表三:

| 表三:本文模擬結果與文獻比較                                                                                                                                                                                             |                    |           |           |                           |                                    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|-----------|---------------------------|------------------------------------|--|--|--|

| Document                                                                                                                                                                                                   | Insertion loss(TX) | P-1dB(TX) | Frequency | Process                   | Technology                         |  |  |  |

| [1] 5.8-GHz CMOS TR switches with high and low substrate resistances in a 0.18-µm CMOS process                                                                                                             | 0.7dB              | 17 dBm    | 5.8GHz    | 0.18-μm<br>CMOS           | p- substrates                      |  |  |  |

| [5]A 900-MHz T/R Switch with<br>a 0.8-dB Insertion Loss<br>Implemented in a 0.5-µm CMOS<br>Process                                                                                                         | 0.73 dB            | 17 dBm    | 900MHz    | 0.5-μm<br>CMOS            | VDB and<br>VSB levels<br>increases |  |  |  |

| [10]A High-Linearity,<br>LC-Tuned, 24-GHz T/R Switch<br>in 90-nm CMOS                                                                                                                                      | 3.4 dB             | 28.7 dBm  | 24GHz     | 90-nm<br>CMOS             | LC-Tuned                           |  |  |  |

| [18] A 15 GHz CMOS RF<br>Switch Employing Large-Signal<br>Impedance Matching                                                                                                                               | 2.08 dB            | 23.62 dBm | 15 GHz    | 0.18 μm<br>SiGe<br>BiCMOS | LC impedance                       |  |  |  |

| [19] Design and analysis for a<br>miniature CMOS SPDT switch<br>using body-floating technique to<br>improve power performance                                                                              | 1.1 dB             | 20 dBm    | 5.8GHz    | 0.18-μm<br>CMOS           | body-floating                      |  |  |  |

| [20] 21.5-dBm power-handling<br>5-GHz transmit/receive CMOS<br>switch realized by voltage<br>division effect of stacked<br>transistor configuration with<br>depletion-layer-extended<br>transistors (DETs) | 0.95 dB            | 21.5 dBm  | 5GHz      | 0.18-μm<br>CMOS           | DET Process                        |  |  |  |

| This work                                                                                                                                                                                                  | 0.538dB            | 27.390dBm | 2.4G      | 0.18-μm<br>CMOS           | Impedance  MEMS  Process           |  |  |  |

未來可繼續往將CMOS開關電路元件再作改善的方向繼續研究,使 CMOS開關電路與無線通訊系統整合的目標更進一步。

## 參考文獻

- [1]Zhenbiao Li; Hyun Yoon; Feng-Jung Huang; O, K.K., "5.8-GHz CMOS T/R switches with high and low substrate resistances in a 0.18-μm CMOS process," Microwave and Wireless Components Letters, IEEE , vol.13, no.1, pp. 1-3, Jan 2003

- [2]Ohnakado, T.; Furukawa, A.; Ono, M.; Taniguchi, E.; Yamakawa, S.; Nishikawa, K.; Murakami, T.; Hashizume, Y.; Sugahara, K.; Oomori, T., "A 1.4 dB insertion-loss, 5 GHz transmit/receive switch utilizing novel depletion-layer -extended transistors (DETs) in 0.18 μm CMOS process," VLSI Technology, 2002. Digest of Technical Papers. 2002 Symposium on , pp. 162-163, June 2002

- [3]Zhenbiao Li; O, K.K., "A 15-GHz integrated CMOS switch with 21.5-dBm IP<sub>1dB</sub> and 1.8-dB insertion loss," VLSI Circuits, 2004. Digest of Technical Papers. 2004 Symposium on , pp. 366-367, 17-19 June 2004

- [4]包克豪,應用於超寬頻無線射頻收發機之CMOS分散式主動射頻積體電路之設計研究,國立成功大學電腦與通訊研究所碩士論文,民國九十五年。

- [5]Feng-Jung Huang; O, K., "A 900-MHz T/R switch with a 0.8-dB insertion loss implemented in a 0.5-μm CMOS process," Custom Integrated Circuits Conference, 2000. CICC. Proceedings of the IEEE 2000, pp.341-344, 2000

- [6]Ali M. Niknejad and Robert G. Meyer, "Analysis of Eddy-Current Losses Over Conductive Substrates with Applications to Monolithic Inductors and Transformers," IEEE Transactions on Microwave Theory and Techniques, vol. 49, pp. 166–176, Jan. 2001.

- [7]C. Patrick Yue and S. Simon Wong, "A Study on Substrate Effects of Silicon-Based RF Passive Components," IEEE MTT-S International Microwave Symposium Digest, vol. 4, pp. 1625–1628, Jun 1999.

- [8] Ching-Liang Dai, Jin-Yu Hong and Mao-Chen Liu, "High Q-factor CMOS-MEMS inductor," Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS, pp. 138–141, Apr. 2008.

- [9]行政院國家科學委員會,微機電系統技術與應用,精密儀器發展中心, 民國93年二版.

- [10]Piljae Park; Dong Hun Shin; Pekarik, J.J.; Rodwell, M.; Yue, C.P., "A high -linearity, LC-Tuned, 24-GHz T/R switch in 90-nm CMOS," Radio Frequency Integrated Circuits Symposium, 2008. RFIC 2008. IEEE, pp.369-372, June 17 2008-April 17 2008

- [11]Naegle, K.M.; Gupta, S.; Allstot, D.J., "Design considerations for a 10 GHz CMOS transmit-receive switch," Circuits and Systems, 2005. ISCAS 2005. IEEE International Symposium on , pp. 2104-2107 Vol. 3, 23-26 May 2005

- [12] Chang-Tsung Fu; Taylor, S.S.; Chien-Nan Kuo, "A 5-GHz, 30-dBm, 0.9-dB insertion loss single-pole double-throw T/R switch in 90nm CMOS," Radio Frequency Integrated Circuits Symposium, 2008. RFIC 2008. IEEE, pp.317-320, June 17 2008-April 17 2008

- [13] Minsik Ahn; Chang-Ho Lee; Byung-Sung Kim; Laskar, J., "A Novel Multi-Stack Device Structure and its Analysis for High Power CMOS Switch Design," Microwave Symposium, 2007. IEEE/MTT-S International, pp.1393-1396, 3-8 June 2007

- [14]Schindler, M.J.; Kazior, T.E., "A high power 2-18 GHz T/R switch," Microwave Symposium Digest, 1990., IEEE MTT-S International , pp.453-456 vol.1, 8-10 May 1990

- [15]Les Besser, and Rowan Gilmore, "Practical RF Circuit Design for Modern Wireless System, Volume I, Passive Circuits and Systems," Artech House, INC., 2003.

- [16] Agilent ADS., Agilent Technology, Available: http://www.agilent.com.

- [17]Rebeiz, G.M.; Muldavin, J.B., "RF MEMS switches and switch circuits," Microwave Magazine, IEEE, vol.2, no.4, pp.59-71, Dec 2001

- [18]Jonghoo Park; Zhenqiang Ma, "A 15 GHz CMOS RF switch employing large-signal impedance matching," Silicon Monolithic Integrated Circuits in RF Systems, 2006. Digest of Papers. 2006 Topical Meeting on , pp.4 pp.-, 18-20 Jan. 2006

- [19] Mei-Chao Yeh; Zuo-Min Tsai; Ren-Chieh Liu; Lin, K.-Y.; Ying-Tang Chang; Huei Wang, "Design and analysis for a miniature CMOS SPDT switch using body-floating technique to improve power performance," *Microwave Theory and Techniques, IEEE Transactions on*, vol.54, no.1, pp. 31-39, Jan. 2006

[20] Ohnakado, T.; Yamakawa, S.; Murakami, T.; Furukawa, A.; Taniguchi, E.; Ueda, H.; Suematsu, N.; Oomori, T., "21.5-dBm power-handling 5-GHz transmit/receive CMOS switch realized by voltage division effect of stacked transistor configuration with depletion-layer-extended transistors (DETs)," *Solid-State Circuits, IEEE Journal of*, vol.39, no.4, pp. 577-584, April 2004